# Exploring Bit-Slice Sparsity in Deep Neural Networks for Efficient ReRAM-Based Deployment

Jingyang Zhang<sup>1</sup>, Huanrui Yang<sup>1</sup>, Fan Chen<sup>1</sup>, Yitu Wang<sup>2</sup>, Hai Li<sup>1</sup> <sup>1</sup>Duke University, <sup>2</sup>Fudan University

# Motivation

### Results

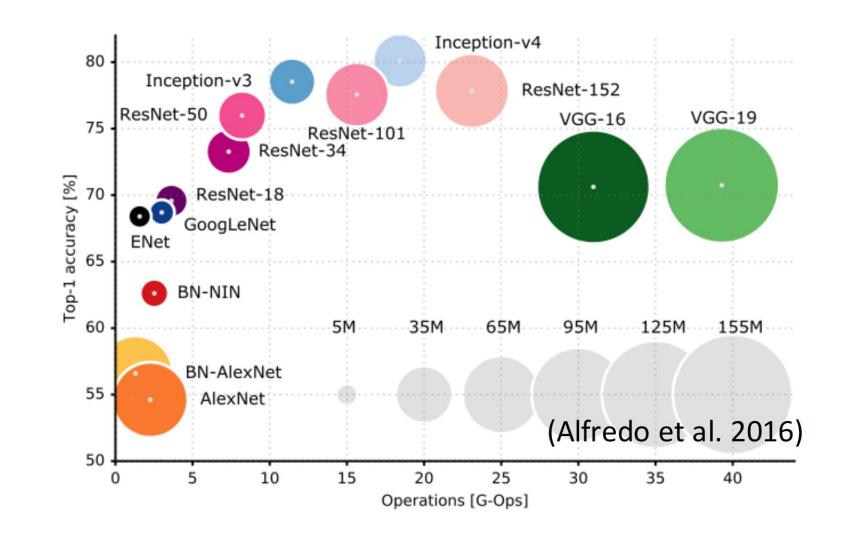

• Deep Neural Network (DNN) models are powerful, but are costly to deploy.

Image Classification on ImageNet

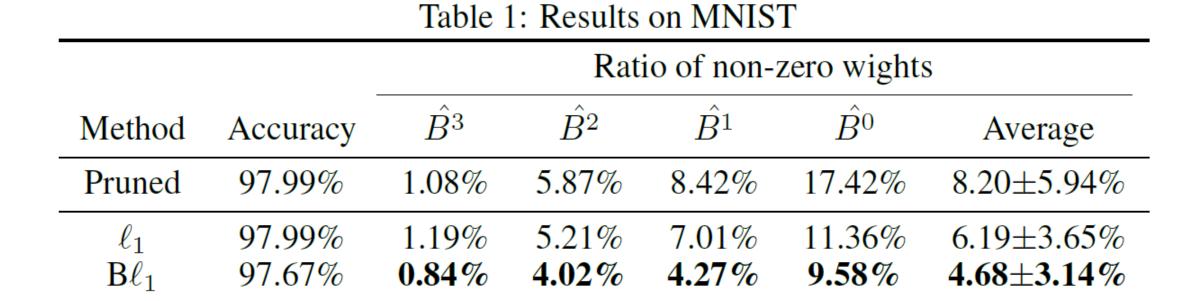

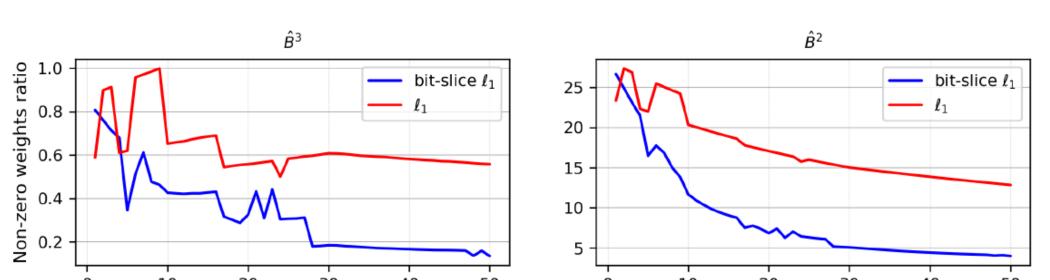

• Significant improvement on bit-slice sparsity

- Resistive random-access memory (ReRAM)-based DNN accelerators (Shafiee et al. 2016, Song et al. 2017)

- In-situ matrix-vector multiplications

- Two-order magnitude advantage in energy, performance and chip footprint

|           |                                                  | Ta                      | ble 2: Res               | sults on CII          | FAR-10                  |                         |                                              |  |  |

|-----------|--------------------------------------------------|-------------------------|--------------------------|-----------------------|-------------------------|-------------------------|----------------------------------------------|--|--|

|           |                                                  |                         | Ratio of non-zero wights |                       |                         |                         |                                              |  |  |

| Model     | Method                                           | Accuracy                | $\hat{B^3}$              | $\hat{B^2}$           | $\hat{B^1}$             | $\hat{B^0}$             | Average                                      |  |  |

| VGG-11    | Pruned                                           | 88.93%                  | 0.86%                    | 28.30%                | 34.14%                  | 33.39%                  | 24.17±13.65%                                 |  |  |

|           | $\begin{array}{c} \ell_1 \\ B\ell_1 \end{array}$ | <b>89.39%</b><br>89.33% | 0.39%<br><b>0.21%</b>    | 9.37%<br><b>3.57%</b> | 18.43%<br><b>7.09%</b>  | 22.19%<br><b>10.71%</b> | 12.59±8.45%<br><b>5.40±3.92%</b>             |  |  |

| ResNet-20 | Pruned                                           | 89.22%                  | 1.10%                    | 8.07%                 | 21.92%                  | 43.96%                  | 18.76±16.36%                                 |  |  |

|           | $\ell_1 \\ \mathbf{B}\ell_1$                     | <b>90.62%</b><br>89.66% | 0.44%<br><b>0.31%</b>    | 4.71%<br><b>3.34%</b> | 14.37%<br><b>11.99%</b> | 33.16%<br><b>31.39%</b> | 13.17±12.60%<br><b>11.76</b> ± <b>12.12%</b> |  |  |

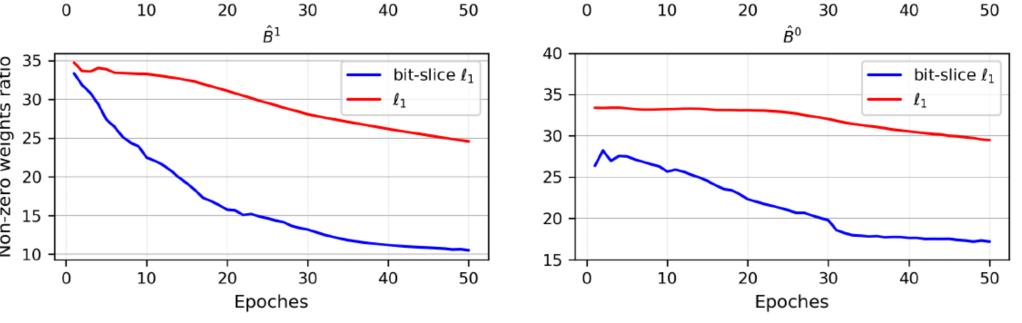

Figure 2: Bit-slice sparsity of VGG-11 on CIFAR-10 during training.

- Reducing ADC overhead on ReRAM-based accelerators

- Map to 128 x 128 ReRAM crossbars (XBs)

| Table 3: ADC Overhead Saving with Bit-Slice Sparsity |                        |                       |               |               |             |  |  |  |  |  |

|------------------------------------------------------|------------------------|-----------------------|---------------|---------------|-------------|--|--|--|--|--|

|                                                      | w/o Bit-Slice Sparsity | w/ Bit-Slice Sparsity |               |               |             |  |  |  |  |  |

|                                                      | Resolution             | Resolution            | Energy Saving | Speedup       | Area Saving |  |  |  |  |  |

| XB <sub>3</sub>                                      | 8 bit                  | 1 bit                 | $28.4 \times$ | $8 \times$    | $2 \times$  |  |  |  |  |  |

| $XB_{2,1,0}$                                         | 8 bit                  | 3 bit                 | $14.2 \times$ | $2.67 \times$ | $2 \times$  |  |  |  |  |  |

Codes available at: https://github.com/zjysteven/ bitslice\_sparsity

### Methods (cont'd)

### Conclusion

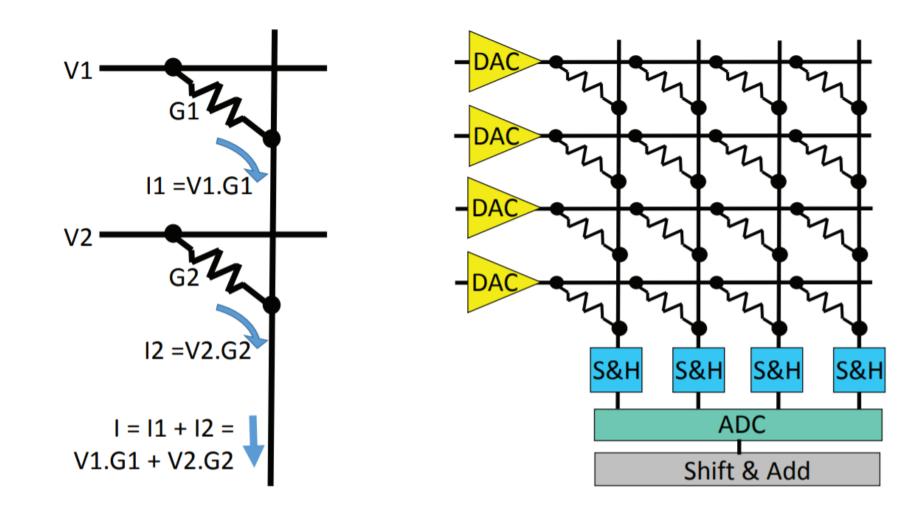

#### (a) Multiply-Accumulate operation

#### (b) Vector-Matrix Multiplier

- Challenges of ReRAM-based accelerators

- Limited cell bit density: operands (i.e. weights) are bit-sliced across multiple ReRAM bitlines

- High bit-resolution ADC accounts for high power (>60%) and area (>30%) overhead

- ADC resolution dictated by accumulated currents on bitlines

- Need *higher sparsity in each bit-slice* to reduce the accumulated current on bitlines, therefore reducing ADC overhead

# Methods

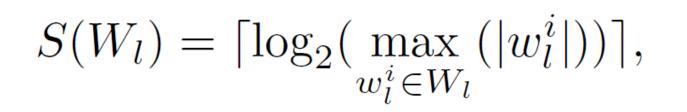

- Dynamic fixed-point quantization

- For each layer, preserve dynamic range

- Bit-slice L1

- Binary representation of the quantized weight

- Slice into 2-bit slices

- L1 regularization across all bit-slices of all elements within a weight matrix/tensor

$B(w_l^i) = \sum_{k=0}^{3} \hat{B}_l^{i,k} \cdot 2^{2k} \qquad B\ell_1(W_l) := \sum_{i,k} \hat{B}_l^{i,k}.$   $\begin{bmatrix} W_l & & Q_{step} \\ 0.1, 0.05 \end{bmatrix} \xrightarrow{2^{-11}} & & B(w_l^0), B(w_l^1) \\ & & 11001100_2 \ 01100110_2 \\ Bl_1(W_l) & & \begin{bmatrix} \hat{B}_l & & & \\ 12 & & & \begin{bmatrix} 3, 0, 3, 0 \end{bmatrix} \\ & & 12 \end{bmatrix} \xrightarrow{k} \begin{bmatrix} 1, 2, 1, 2 \end{bmatrix} \xrightarrow{k} \begin{bmatrix} bit-slice \ l 1 \end{bmatrix}$

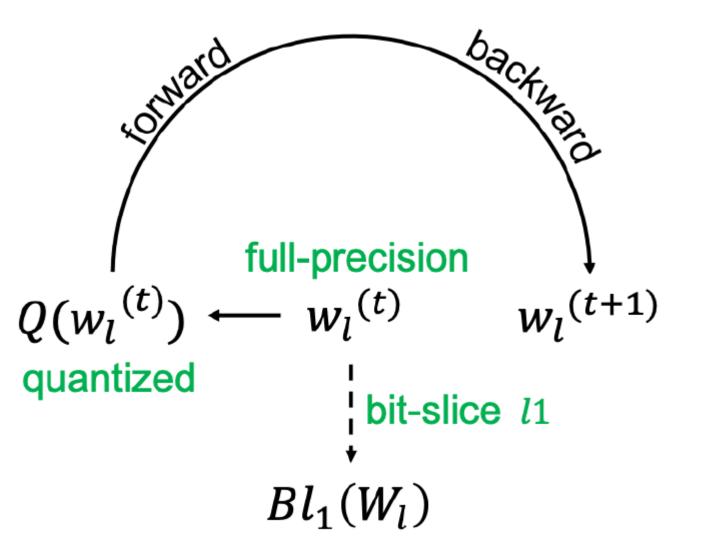

- Overall training routine

- Forward and backward pass with quantized weight, gradient update on full-precision weight

Add bit-slice L1 to the objective

- We propose *bit-slice L1* regularizer, the first algorithm to induce bit-slice sparsity during the training of dynamic fixed-point DNNs

- *Up to 2x or more* sparsity improvement on bit slices comparing to traditional L1 regularizer

- When deployed on ReRAM-based accelerator, the achieved bit-slice sparsity allows the ADC resolution to be *reduced to 1-bit* of the most significant bit-slice and *down to 3-bit* for the others bits, which significantly reduces power and area overhead.

# Acknowledgement

This work was supported in part by NSF CNS-1822085 and NSF CSR-1717885.

• Uniform n-bit quantization after scaling

$Q_{step} = 2^{S(W_l) - n}, \qquad B(w_l^i) = \lfloor \frac{w_l^i}{Q_{step}} \rfloor.$

- $B(w_l^i)$  will be stored on ReRAM crossbar

- Dynamic range recovery

$Q(w_l^i) = B(w_l^i) \cdot Q_{step}$

- Recovery can be done efficiently with shifting

- $Q(w_l^i)$  will be used for computation

$q^{(t)} = Q(w_l^{(t)}),$

$w_l^{(t+1)} = q^{(t)} - lr \times (\nabla_q \mathcal{L}_{CE}(q^{(t)}) + \alpha \nabla_q B\ell_1(q^{(t)}))$

## References

•

•

•

- A. Shafiee, A. Nag, N. Muralimanohar, R. Balasubramonian, J. P.

Strachan, M. Hu, R. S. Williams, and V. Srikumar. Isaac: A convolutional neural network accelerator with in-situ analog arithmetic in crossbars . In Proceedings of ISCA, 2016.

- L. Song, X. Qian, H. Li, and Y. Chen. Pipelayer: A pipelined rerambased accelerator for deep learning. . In Proceedings of HPCA, 2017.

- T. Yang, H. Cheng, C. Yang, I. Tseng, H. Hu, H. Chang, and H. Li. Sparse reram engine: Joint exploration of activation and weight sparsity in compressed neural networks. In Proceedings of ISCA, 2019.

- P. Gysel. Ristretto: Hardware-oriented approximation of convolutional neural networks. arXiv preprint arXiv:1605.06402, 2016.

- M. Saberi, R. Lotfi, K. Mafinezhad, and W. A. Serdijn. Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation adcs. IEEE Transactions on Circuits and Systems I: Regular Papers, 2011.

The 5th Workshop on Energy Efficient Machine Learning and Cognitive Computing @ NeurIPS 2019