# Moving CNN Accelerator Computations Closer to Data

Sumanth Gudaparthi Surya Narayanan Rajeev Balasubramonian

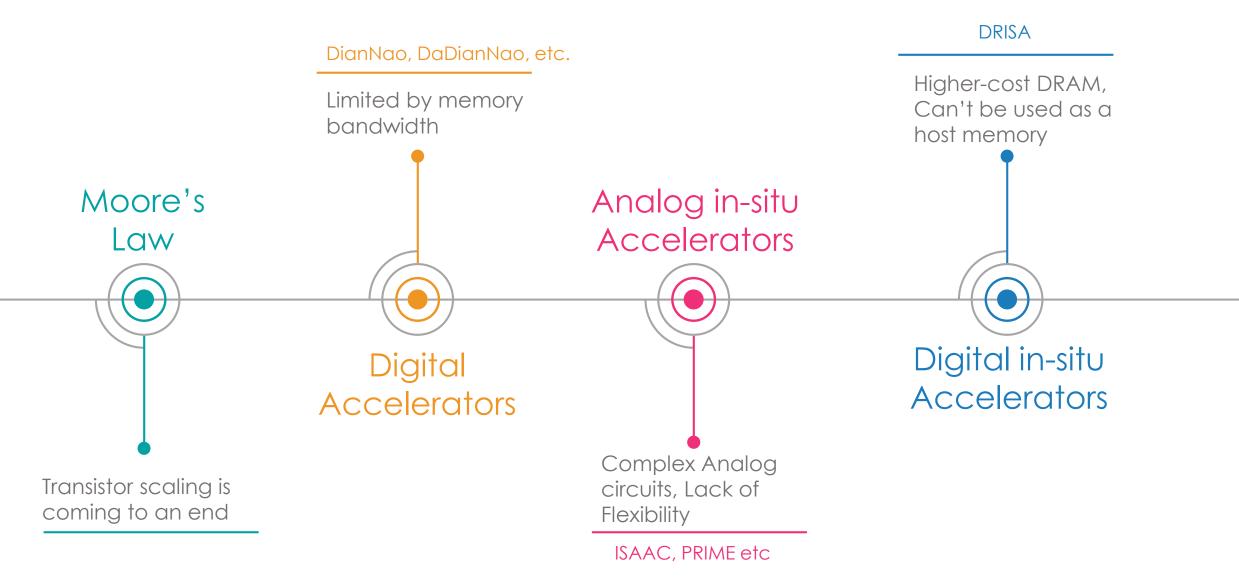

### Evolution of CNN Accelerators

### SRAM based In-Situ Computation Accelerator

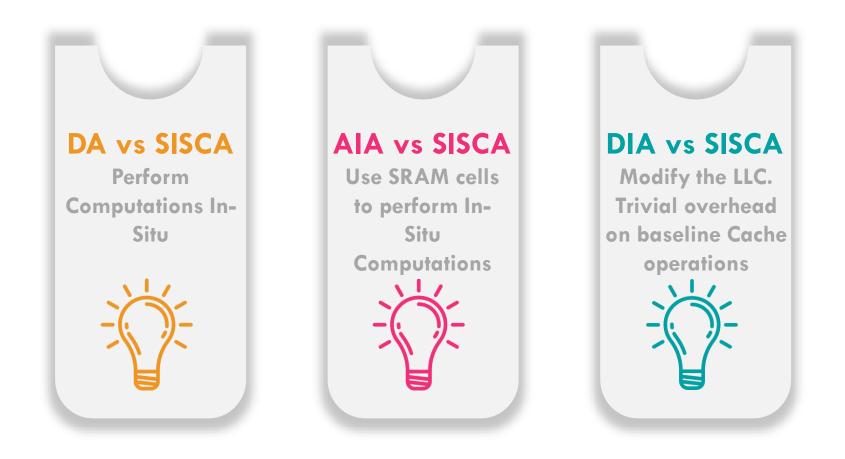

SISCA: Proposed Accelerator DA: Digital Accelerators AIA: Analog In-situ Accelerators DIA: Digital In-situ Accelerators

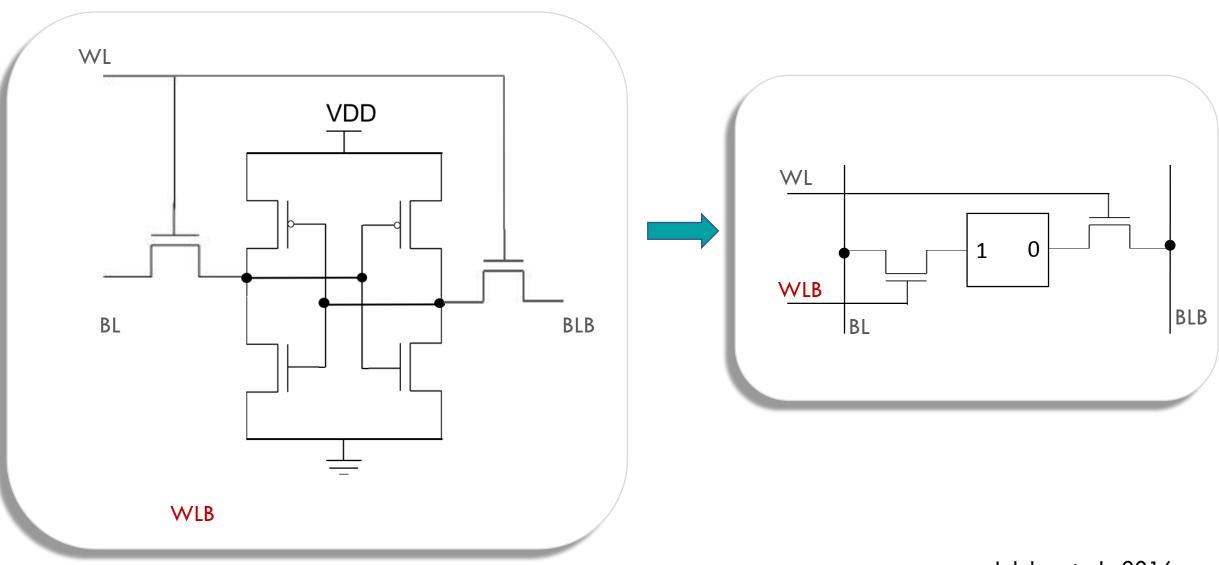

#### Logic-In-Memory

Jeloka et al., 2016

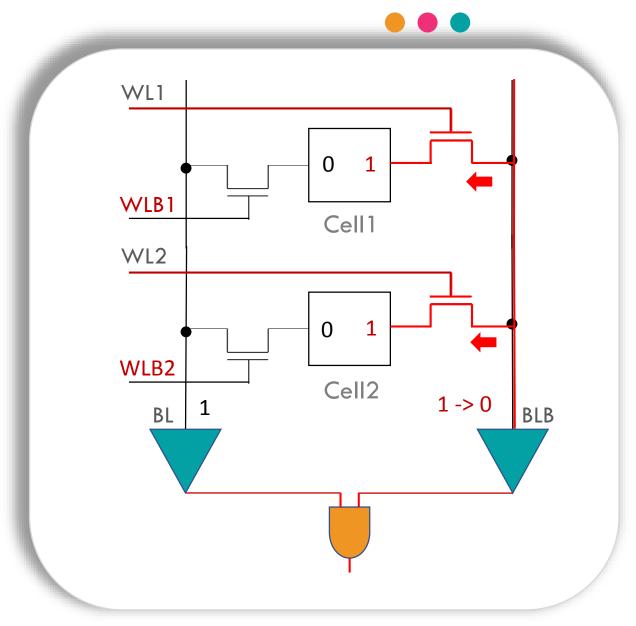

#### Logic-In-Memory

Pre-charge the bit-lines Activate the word-lines Discharge of bit-line voltage through Cell1 Discharge of bit-line voltage through both Cells Bit-line stays Pre-charged

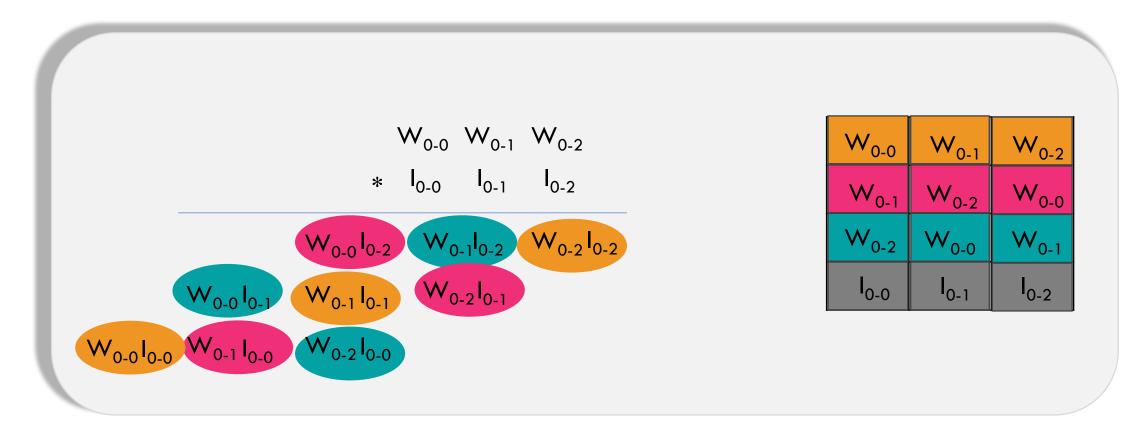

# Enabling In-Situ Multiplication in Caches

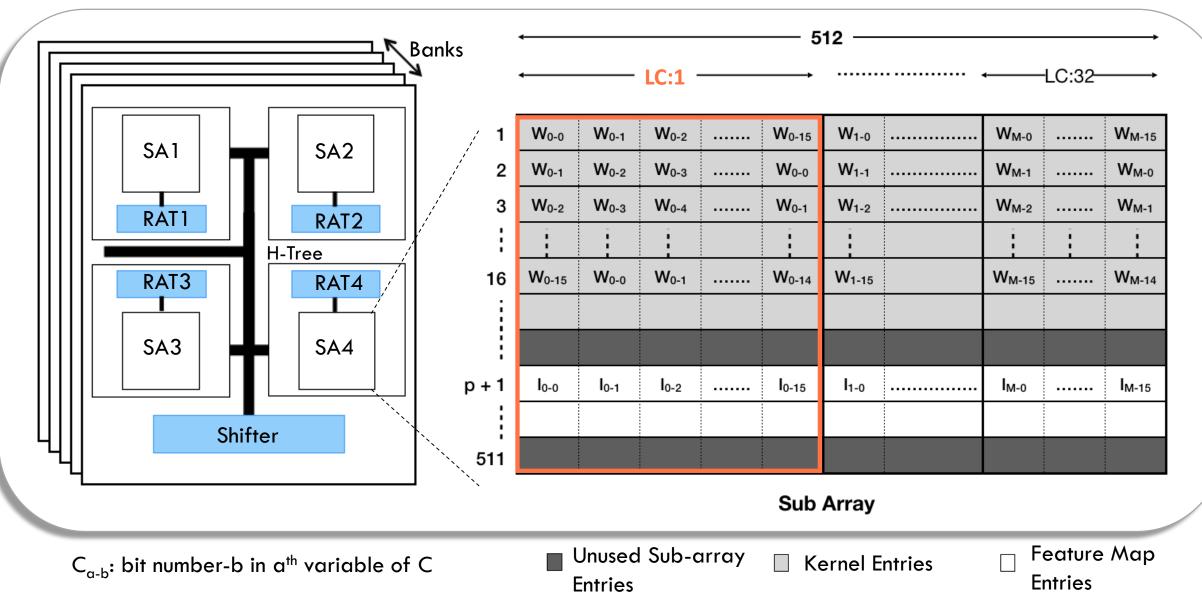

#### SISCA Organization

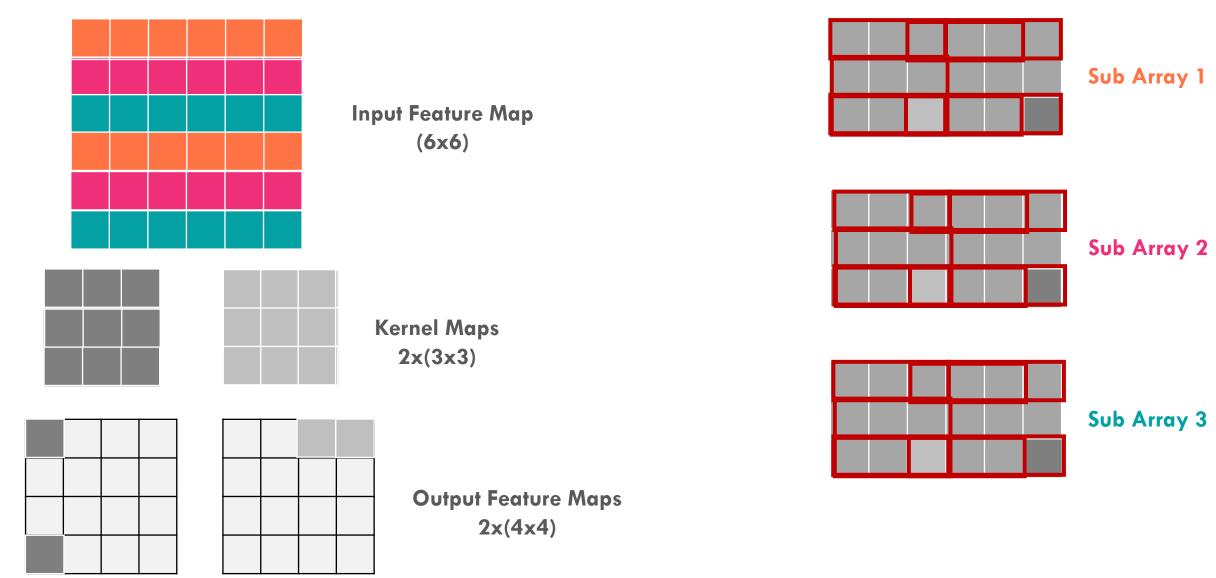

### SISCA Dataflow

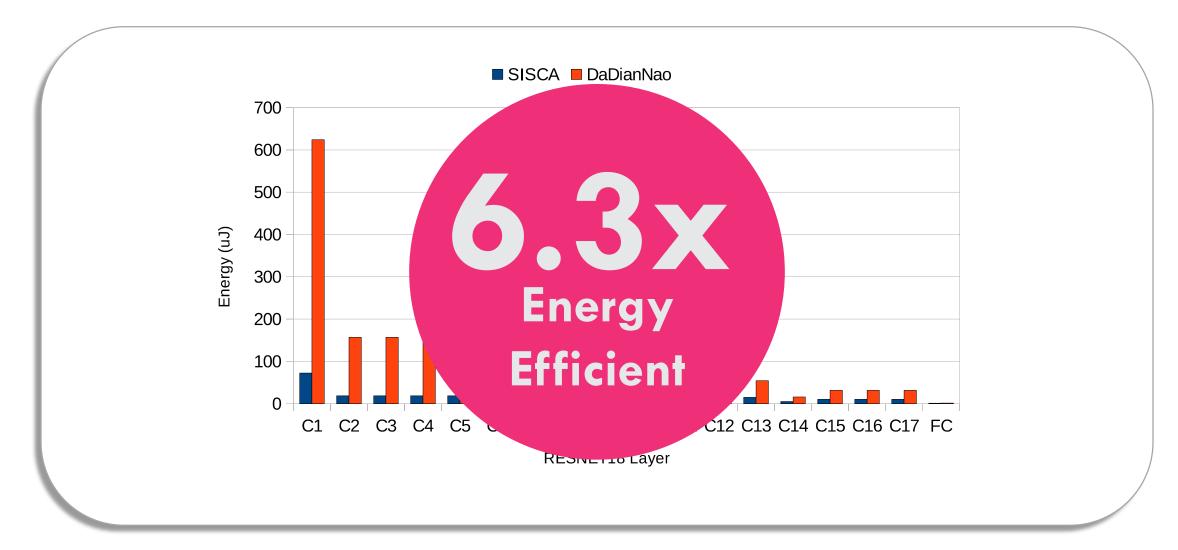

## Energy Improvements

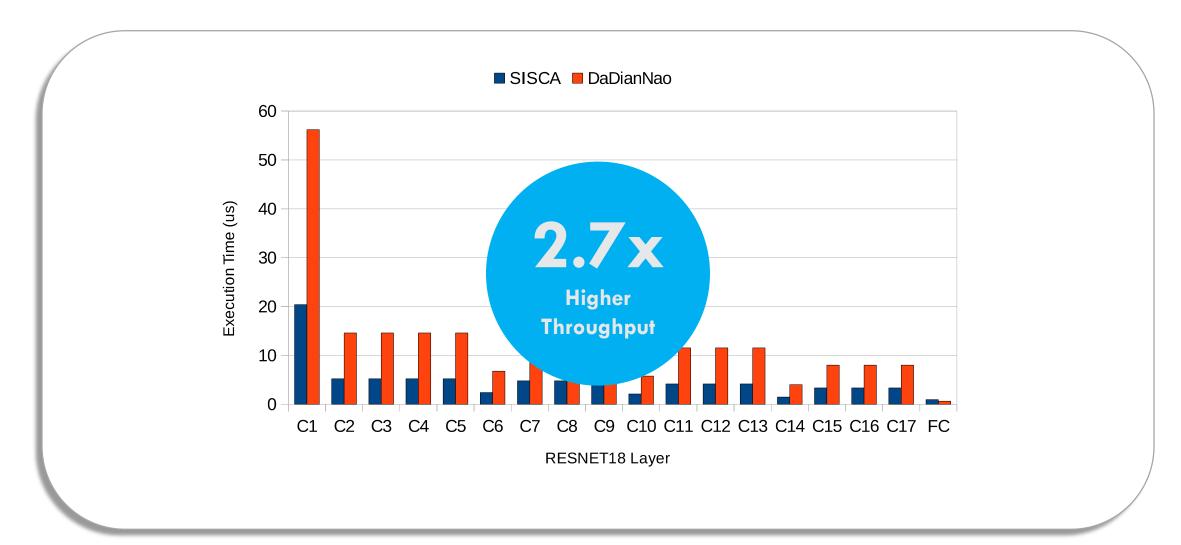

### Performance Improvements

## Conclusions and Future Work

- SISCA is an SRAM in-situ computation Engine for Convolution Neural Networks

- Uses on-chip Last Level Cache (LLC) to perform computations

- SISCA is 6.3x Energy efficient, and has 2.7x higher throughput than DaDianNao

- Better dataflow and mapping mechanisms can further improve the Energy and Throughput.

- Need to work on better scheduling mechanisms to distribute the general purpose workload, and CNN data across the Cache.